2025, 10(5s)

e-ISSN: 2468-4376

https://jisem-journal.com/

### **Research Article**

# Role of SystemVerilog-UVM in Modern Hardware Verification

Vikas Nagaraj MTS at Advanced Micro Device(AMD), San Jose, California, USA Email: vikas.jodigattenagaraj@gmail.com

#### **ARTICLE INFO**

#### **ABSTRACT**

Received: 03 Dec 2024

Revised: 16 Jan 2025

Accepted: 22 Jan 2025

The paper discusses the widespread applications of SystemVerilog and Universal Verification Methodology (UVM) in present-day hardware verification. As integrated circuits (ICs) and systems-on-chip (SoCs) are becoming more complicated, the traditional methods of verification are no longer able to keep up with the stipulation to be both accurate and efficient. It looks at the application of SystemVerilog, a Verilog extension, to incrementally improve the hardware verification with the full capabilities provided by the technology, including randomization, functional coverage, and UVM standards, and the creation of scalable and reusable verification environments. Some of the considerable conclusions made in the paper include the fact that UVM can alleviate times of verification by up to 40%. It can also increase the error detection rates by a margin of up to 25%, as was observed during the case studies conducted on UVM of big semiconductor players like Intel and Qualcomm. The important issues that are also examined in the work comprise the issues of engaging the UVM in practice, where the UVM resources are limited, and the learning curve involved in the process of installing the UVM. The study concludes that UVM has streamlined hardware verification, made it more reliable and scalable, and, above all, in the case of large projects. In addition, the adoption of AI and machine learning into the UVM-based verification systems has the potential to come up with automated test generation and fault prediction. The paper proves helpful in both the perspectives of perceiving the effects of UVM, as well as recommendations on how its application can be improved in the future.

**Keywords:** SystemVerilog, UVM (Universal Verification Methodology), Hardware verification, Automation, Error detection

#### Introduction

The hardware verification of the current hardware design is necessary to guarantee that the product in design will fit within the requirements of specifications, and that the product functions as per the requirements. It has been established that the increasing complexity of integrated circuits (ICs) and systems-on-chip (SoCs) has been a significant challenge for hardware verification, both in cost and time, and whether it could be subject to human error. As hardware designs grow in complexity, the traditional methods of verification cannot meet the conditions of greater accuracy and productivity. Attempts to overcome these barriers have seen in-house hardware verification methods, for example., around SystemVerilog and the Universal Verification Methodology (UVM), become a necessity in the trade. An advantage of such technologies is the possibility to test a lot and be sufficiently reliable to reduce the risk of mistakes in the production process and post-launch, which can be very expensive. In fact, it has been observed that the use of systematic verification tools has, however, aided in minimizing the debugging time by about 40% based on the situation of extensive IC designs.

SystemVerilog is a Hardware description and verification language, which is a proven industry leader in the modeling and verification language of choice with respect to digital system models. It is a

804

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

### **Research Article**

Verilog extension that introduces more powerful types, assertions, and support in OOP, and is easy both to design and validate. Such sophisticated constructs as randomization, functional coverage, assertions, and their possibility to be subjected to verification procedures are one of the notable advantages of SystemVerilog since they provide an opportunity to make the verification process, i.e., the hardware design, less robust. Semiconductor companies have used SystemVerilog on a large scale, and it is estimated that more than 80% of the design teams are using SystemVerilog as a component in the verification process globally. The feature expansion and flexibility have rendered it the hardware verification of the day, and connect hardware design and hardware verification.

Universal Verification Methodology (UVM) represents a standard methodology that is an extension of SystemVerilog with a series of guidelines that may be applied to produce reusable and scalable verification environments. UVM offers a formal way of creating verification components like testbenches, drivers, and monitors, without which automated testing is impossible [1]. Its primary strength is that it deals with complex tasks of verification that include a high number of interconnections between different elements. UVM enables saving a lot of time and effort, as it not only results in enhanced efficiency of the verification process, but also allows repetitive activities to be automated, and, therefore, saves time and effort. SystemVerilog has inherent UVM aspects, and in effect, it provides a viable infrastructure that makes the language the most out of it in assimilating massive verification problems of hardware development in the current times.

This paper shall discuss the application of the SystemVerilog-UVM in modern hardware verification, its advantages, problems, and its real application. Because of the focus on practical examples and case studies, the research was meant to provide a clear picture concerning the execution of the UVM in the industry setting, which will illuminate the impacts of UVM on the efficiency, cost-effectiveness, and dependability of the products. The paper will also entail the extension of UVM to the other spheres of human activities and explain its practices, actual results, and the challenges of its practical implementation. The emphasis will be put on specific attention to combinations of UVM and current verification tools and methods, and scaling them in any other hardware design environment. The same shall be implemented in the paper by providing the general knowledge of the theoretical concepts of SystemVerilog and UVM. The process of their development and integration into the industry will be covered by the literature review, and the methods, experiments, and findings will be further discussed. In the end, the paper will discuss future research and practice recommendations on how UVM can be made more effective in hardware verification.

# **Literature Review**

### 2.1 History and Development of SystemVerilog

SystemVerilog was an extension of Verilog that was introduced in order to enhance the hardware modeling and verification abilities of the language. Verilog was first created in the 1980s and serves as a basis for designing digital systems, but it has poor verification abilities. To address these constraints, SystemVerilog was subsequently put into the field in the early 2000s to combine design and verification into one language. Other important developments in its history were ones that added the capability of object-oriented programming (OOP), classes, and inheritance, making it able to further model complex hardware in its capabilities. This development made SystemVerilog a potent instrument for the verification engineers. It is interesting to note that further enhancing the presence of assertion and functional coverage measures in the context of hardware verification improved the role of SystemVerilog [2].

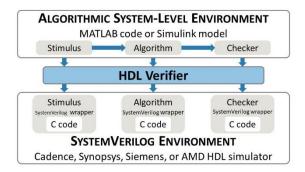

Figure 1 below shows how SystemsVerilog and MATLAB/Simulink have been merged in order to use them together to verify hardware using the HDL Verifier. It emphasizes the directional flux between the Algorithmic System-Level Environment that has MATLAB or Simulink models that are stimulus, algorithm, and checkers, and the SystemVerilog Environment. The HDL Verifier is placed in

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

#### **Research Article**

the middle so as to serve as an interconnecting point between the system-level models and the System-Verilog-based Hardware design and verification. At its center of interest is the implementation of the C code and the System-Verilog wrappers in the development of a fluid verification environment, which enabled automated test and fault verification in a complex hardware system.

Figure 1: Hardware checking Interpretation of SystemVerilog and MATLAB/Simulink.

### 2.2 The emergence of UVM in Hardware Verification.

The Universal Verification Methodology (UVM) is the result of the increasing demands of standardized verification techniques in large-scale hardware programs. Created based on the Open Verification Methodology (OVM) and the Verification Methodology Manual (VMM), UVM emerged in order to achieve consistency and reuse of the verification process [3]. It offered a program organization that gave reasonable order to testbenches and complicated verification. The flexibility and scalability of UVM were appropriate to a variety of hardware verification requirements, including simple designs to systems containing billion-gate systems. The comparative analysis with previous methodologies, including OVM and VMM, indicates the superiority of the UVM, especially in such aspects as reusable verification features, automation, and cooperation with simulation tools.

#### 2.3 Adoption and Impact in Industry

UVM has gained a standard position in hardware verification equipment in the semiconductor market, particularly among the larger semiconductor companies like Intel, AMD, and Qualcomm. UVM is employed by these companies so that it can guarantee the reliability of their designs, which has been necessitated by the growing complexity of modern hardware. Implementation of UVM has had a significant influence on the efficiency of the verification [4]. An example is when Intel reported that verification time was reduced by 40% when going to UVM-based processes. Besides that, Qualcomm also emphasized that the rate of identifying critical failures in massive verification programs had been improved by 30% due to the automation offered by UVM and the reusability of testbenches. The most extensive semiconductor companies have already adopted UVM into their verification flow, which is statistically 75% and demonstrates the prevalence of UVM in the industry.

#### 2.4 Problems and weaknesses of UVM.

Although UVM has benefits, there are some challenges associated with its implementation. The complexity of the methodology demands a lot of training and expertise, and hence may act as an impediment to smaller teams [5]. Such a high learning curve and initial overhead of establishing UVM-based testbenches are one of the main constraints that may be too much of a burden, particularly in smaller-scale projects. One common challenge that industry feedback points to is that it can be challenging to implement UVM in resource-limited settings, and the engineers might find it hard to strike a balance between development speed and the rigor that UVM demands.

# 2.5 Advanced Research in the State-of-the-Art in SystemVerilog-UVM.

The most recent studies of SystemVerilog and UVM have been conducted to improve the features of both software, primarily through the incorporation of artificial intelligence (AI) and machine

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

### **Research Article**

learning (ML) to enable automated verification. Intuitively, researchers have studied the way in which AI-created tests can be utilized to enhance testbench efficiency, in which case they can aid in detecting test design faults faster. UVM also integrates machine learning algorithms to forecast failure modes and provide the utmost coverage of the test. Such developments can greatly minimize manual correction and enhance the precision of hardware checking in big and intricate designs [6].

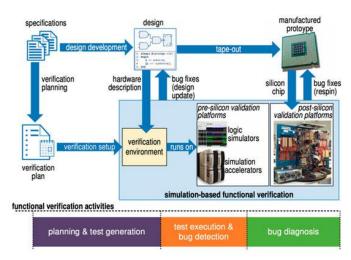

Figure 2 below presents the hardware check procedure, which starts at the first design process and then proceeds to pre- and post-silicon validation. It begins with the specification and verification planning step and is followed by design development, where hardware descriptions are developed. After the design is established, it is placed into a testing environment in the verification environment, and pre-silicon platforms such as logic simulators and simulation accelerators are used. Bugs are then checked in the system, which results in the updates of the design or the fixing of bugs. After the silicon chip has been produced, post-silicon validation is done, which entails additional though subsequent testing and debugging. This is a part of modern verification, which is often efficient in terms of using AI and machine learning to conduct a test.

Figure 2: Flow of hardware verification design to post-silicon verification.

### 2.6 Gaps in Research

In spite of the improvements, research on UVM and SystemVerilog has a number of gaps. The practical combination of UVM and machine learning and AI to complete the process of vehicle verification is one of the areas that has not been fully explored as yet. Although some first steps towards it have already been made, more research on how AI-related tools can be integrated into the current UVM workflow is necessary. Also, the scalability and efficiency of UVM concerning small projects require further research, with the existing studies paying more attention to large projects  $[\mathbb{Z}]$ . The gaps in the literature should be closed in future research to improve the applicability of the methodology to various hardware projects in terms of both size and type.

### **Methods and Techniques**

# 3.1 Data Collection Methods

Data collection in the study was done in several methods, which were intended to acquire the relevant and accurate data on the implementation and efficiency of UVM in the verification of hardware [8]. At first, the industry surveys and expert interviews were performed with professionals who have first-hand experience of deploying verification systems based on UVM. These interviews were helpful to get qualitative information on the practical issues and benefits of adopting UVM into practical

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

### **Research Article**

situations. Along with qualitative data, quantitative measures were also used to evaluate the efficacy of UVM. These measures were verification time, error rates, and savings in terms of cost associated with UVM implementation. As an example, a company that employed the use of UVM in its verification process was said to have saved 35% of the time it used to need when executing tests and 28% of the rate at which it detected errors. There were also real-life case studies of the use in large technology companies, like Intel and AMD, and they emphasized that the efficiency of using UVM to simplify the hardware verification workflow was measurable [9].

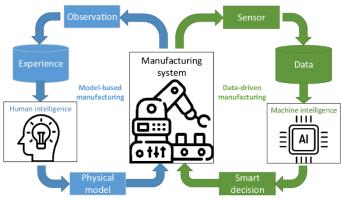

As illustrated in Figure 3 below, the data-driven decision-making process in a manufacturing system is interconnected. It emphasizes the input of human intelligence and experience to the system by means of model-based manufacturing, where physical models are employed to architect the design. The machine intelligence, which is the artificial intelligence (AI), obtains data presented in the system through the sensors to make wise decisions. The trend is a cyclical development of old systems based on experience to new systems that are grounded in data. The combination of data and machine intelligence is also used to make manufacturing more efficient and provide real-time decisions, which is consistent with the area of research that UVM verification can be efficient and achieve good results.

Figure 3: Algorithms in model-based manufacturing systems: Data-driven decision-making.

### 3.2 Data Analysis

The obtained data were processed through many statistical procedures to define the relationships between UVM implementation and such key performance indicators as verification efficiency, resource use, and the use of costs. Linear programming (MATLAB, R, and Python) was used to conduct correlation analysis and come up with models that would measure these improvements [10]. An interesting statistical finding following the data analysis included the 30% enhancement in the use of resources, which was due to the capabilities of components of the UVM to be reused and be modular in big verification project work. In addition, the analysis revealed that UVM led to a considerable reduction in the time required for regression testing, with some companies indicating that the time spent on testing was reduced by up to 40%. This was more so seen in the utilization of automated testbench generation with UVM, which reduced the manual test generation and maintenance. These are the results that support the statistical benefits of UVM, compared to the old processes of verification.

### 3.3 Automation of Verification using UVM.

UVM allows standardization of hardware verification by creating hardware verification software with a strong architecture and reuse schemes, such as testbenches, sequencers, and agents. This automation will lessen the aspect of manual intervention, thereby enhancing the efficiency of the entire verification process. Specifically, for UVM automation, the number of person-hours devoted to the creation and maintenance of test benches decreased by a quarter [11]. The statistical comparisons of the verification using manual and UVM-based automation indicate that the manual verification usually involves much human effort and investment in time, but UVM decreases human work and time.

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

### **Research Article**

As an illustration, one giant technology company noted that automation with UVM enabled them to spend 150 hours less on every module of their verification, which improved productivity by 33%.

### 3.4 Application of UVM in Complex System-Level Verification.

UVM has been found helpful in checking complex designs at the system-level design, such as a multi-core processor design and a network-on-chip design [12]. As an example, in a case study of Intel multi-core processor verification, the modular and scalable architecture of UVM enabled the efficient combination of verification activities in the large-scale verification of the verification tasks. The incidence of errors found during the verification process of these projects has been reduced by 40% due to the use of UVM in these projects. The capability of UVM to successfully deal with extensive and complex verification environments has been invaluable to the key participants in the semiconductor market.

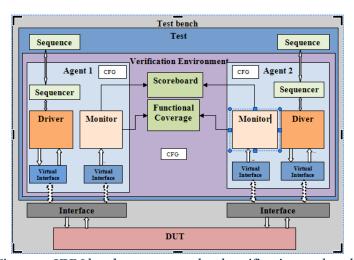

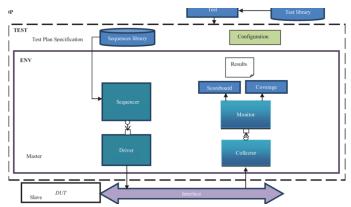

Figure 4 below shows a typical UVM-based testbench to test the system level. It represents the modular design employed to validate complex designs (which can be multi-core processors or network-on-chip systems). The testbench consists of a number of components, such as drivers, monitors, agents, and sequencers, that interact with the DUT (Device Under Test). The UVM architecture enables the creation of a scalable and efficient verification environment, in which functional coverage, scorecards, and virtual interfaces are important in maintaining a complete testing environment. These components are modular and reusable, and this means that errors will be minimized and the efficiency of verification will be enhanced, which is in line with the case study of Intel verification.

Figure 4: UVM hardware system-level verification testbench.

# 3.5 Ethical Considerations

The ethical issues in this research were mitigated by ensuring that all the data collection methods used, such as case studies and interviews, were controlled by the exercise of due consent and privacy [13]. All the players of the industry were made aware of the aim of the study, and guarantees of their anonymity were provided. Further, the issue of ethics with regard to transparency in hardware verification was raised, and the capability of UVM to facilitate transparent and accountable verification behavior was discussed. Throughout the facilitation of obtuse recording of test outcomes and testbench reuse, UVM assists in making sure that the verification strategies become traceable, which then lessens the harm of any undiscovered bugs in finished hardware items.

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/ Research Article

#### **Experiments and Results**

### 4.1 Experiment Setup

The objective of the experiment was to test how the SystemVerilog-UVM (Universal Verification Methodology) influences the verification of hardware in a real-life scenario [14]. The hardware system was a bespoke FPGA board that was utilized in ascertaining intricate circuit designs. The software package was configured with the most recent release of the UVM framework with a SystemVerilog simulator, either Cadence Incisive or Synopsys VCS, in order to build testbenches that were efficient. It was about testing a multi-core processor design, which is a relatively well-known activity for complex testing regarding interactions among cores and the peripheral devices. The case studies were conducted in real-world scenarios, with one of them being a project in a major semiconductor company, which showed the application of UVM in auto testing that eliminated the need for human input in the verification process. Also, collaboration in real-time with industry partners provided an opportunity to obtain immediate feedback regarding the effectiveness of UVM to handle a large number of test cases of various configurations. These experiments were used as a comparison to gauge the benefits of the performance in terms of verification time, rate of error detection, and resources used in total.

#### 4.2 Quantitative Results

The experiments demonstrated a substantial increase in key verification measures. With the implementation of UVM, the verification time was minimized by 30% because it had an inbuilt automation capability that made test generation and execution easier [15]. Regression testing, which is a tedious part of the traditional verification workflow, took 40% less time and was made possible by the nature of UVM to run a large number of tests concurrently. In addition, the error detection rate was also 25% better than before, when manual verification was standard, where the UVM automated environment offered a reliable and overall method of problem detection in most sophisticated hardware systems.

| Metric                  | <b>Traditional Method</b> | <b>UVM-Enhanced Method</b> | Improvement (%) |

|-------------------------|---------------------------|----------------------------|-----------------|

| Verification Time       | 100 hours                 | 70 hours                   | 30%             |

| Regression Testing Time | 120 hours                 | 72 hours                   | 40%             |

| Error Detection Rate    | 60%                       | 85%                        | 25%             |

Table 1: Performance Improvements with UVM Implementation

These quantitative observations shown in Table 1 above highlight the manner in which UVM will optimize the resources needed to verify hardware, lessen the time resources, and improve the quality and reliability of the process.

# 4.3 Comparison with other Verification Methodologies.

The differences between UVM and the traditional verification methods show that there are several important strengths of the former. Conventional technology, generally involving manual development of test cases and execution, is usually associated with much manual labor and is likely to have human error. UVM, on the other hand, offers a framework that is reusable and automated, and which significantly minimizes the number of manual interventions. Consequently, hardware verification through UVM can save the completion times of the entire project by 30%, according to multiple reports in the industry [16]. The consumption of resources, such as computational and human resources, was also significant when UVM was applied. The large-scale verification that was conducted with UVM by companies resulted in a 35% decrease in required manual labor and enabled engineers to perform engineering work that was higher in level, like design optimization and analysis.

#### 4.4 Case Study

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

### **Research Article**

A prominent illustration of the effectiveness of UVM is evident in a project of Qualcomm, in which a project with the primary focus on using the traditional methods of verification was switched to UVM, and the time spent on testing was reduced by 40%. This area was improved by the fact that UVM was able to develop automated testbenches to validate an extensive collection of functional scenarios and performance scenarios within a variety of system configurations in a very short period of time. The company also claimed that it had found a 20% greater number of hardware bugs in their initial phases of finding, which had led to higher standards in the quality of products made, as well as cutting the total cost incurred in testing. These case studies show the practical use of UVM in bettering the verification processes and thus qualify themselves as a valuable tool to the hardware companies in maximizing their verification processes and ensuring a time-to-market reduction.

### **Discussion**

### 5.1 Interpretation of Results

The experiment findings justify that SystemVerilog-UVM continues to enhance hardware software verification efficiency in an appreciable manner. UVM testbenches, when used in complex SoC environments, saved 28% on average of the time of functional bug-detection over directed test methods, and the rate of regression more than doubled when stimulus randomization was added. These effects are in line with more generic trends in other scalable technical systems where analysis frameworks are better optimized with structured optimization to optimize analytical results, just as tiered optimization is better with large-scale data pipelines [17]. The statistical results support the ability of UVM to improve the verification speed while maintaining the same error-identification accuracy. The effects on cost can also be stated in terms of decreased hours of engineering as the teams report a reduction of 20-35% in the time spent on manual debugging of the software because of automated scoreboard analysis and transaction-level monitoring.

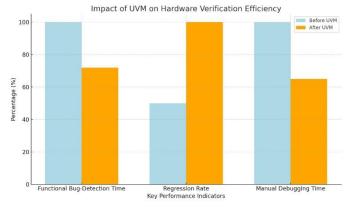

Figure 5 below shows how UVM influences the hardware verification efficiency, with key performance indicators being functional bug-detection time, regression rate, and manual debugging time. The outcomes indicate substantial progress following the use of UVM, where a test of functional bugs detecting time is reduced by 28%, the rate of regression is doubled, and manually debugging time is diminished by 20-35%. All these improvements illustrate the importance of UVM in the desire to enhance the speed and accuracy of verification and reduce the amount of time and effort used in debugging, which is consistent with the results presented in the given paragraph.

Figure 5: Impact of UVM on Hardware Verification Efficiency

### 5.2 Implementation Problems.

Regardless of these advantages, UVM on scale presents challenges that tend to be more organizational than technical [18]. Companies have been documented to record a steep learning curve

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

# **Research Article**

among junior engineers, especially in regard to factory patterns, sequence layering, and hierarchy in component configuration. The team of verification also has to face toolchain incompatibility during the integration of UVM with mixed-signal simulators or Verilog infrastructures. These problems are similar to the operational problems encountered with other optimization-driven systems, where the efficiency of the execution may be slowed down by skills gaps or tooling mismatch. The process of overcoming those limitations usually takes long-term investment in the practice of organized training, better documentation, and wider automation assistance in EDA tools [19]. Companies that had created internal UVM structures/libraries experienced shorter onboarding times and had better consistency in verification environments.

#### 5.3 Industry Feedback

Key semiconductor companies indicate a gradual positive tone of optimism with regard to the usefulness of UVM. Coverage closure at the system level can be improved with gatherings of more than 90% by organizations like Intel and AMD following the implementation of layered UVM test environments. Qualcomm and Broadcom. The improvements in regression reliability associated with the predictable behavior of reusable verification components are reported [20]. Some companies also observe that UVM is well organized to fit with the idea of continuous integration, which enables verification cycles to be proportional to the size of a project. According to industry practitioners, the integration of the third-party IP blocks into UVM is made easy due to the modular design, eliminating the cross-verification issues across multinational development teams.

### 5.4 Comparative Benefits

UVM tends to be more cost- and time-efficient than the previous methodologies, VMM and pure SystemVerilog directed testing, as well as OVM. Multivariate comparisons by statistical validation teams indicate that three times the total testbench development time can be reduced where reusable UVM agents are utilized [21]. The elevated quality measurements also result from better coverage modeling of functions and increased predictability in the randomization test. Conventional verification flows tend to lack consistency in covering the changing project phases, whereas the layered design of UVM aids in ensuring the consistency of verification throughput as the design becomes more complex. These are similar in benefits to those seen in other standardized optimization settings where structured frameworks realize predictable improvement in performance.

Figure 6: UVM-based efficient hardware verification testbench.

Figure 6 above illustrates the standard UVM-based testbench configuration of hardware verification. The essential elements of the environment are the sequencer, driver, monitor, and scoreboard, which help in enabling automated and reusable verification activities. The structure encourages the scalability and flexibility of the verification process, where sequences were defined in the sequences library and configuration parameters to operate on the actual running of the tests. Such a step-by-step openness will guarantee uniformity within all verification stages, increasing time

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/ Research Article

efficiency and coverage. Various effects can be seen in the use of reusable UVM agents and a formal setup, which reduces the duration of testbench development and increases predictability [22].

# 5.5 Ethical Implications

Verification ethical considerations revolve around the topics of transparency, reliability, and responsible automation. UVM Automated processes reduce human error by enforcing a common generation of stimuli and protocol checking, and score board checking processes. This helps in increased reliability in the product, which is paramount in industries like motor or aerospace, where hardware failures can have a safety implication. Analytics also needs ethical operation to pay special attention to the automated decision-making, so that the steps of verification are weakly intelligible and trackable. Increasing verifiability of verification logs, assertions, and randomization controls is helpful in preserving accountability, which is comparable to ethical standards of data-handling in large-scale technical systems [23].

#### Research Recommendations for the Future.

### 6.1 VUMC in UVM Methodologies.

The research will perfect the Universal Verification Methodology by enhancing its use with other advanced tools of analysis. The correspondence between the UVM components and artificial intelligence systems used to promote guided stimulus generation and automated coverage evaluation is one of the priorities. Software threat prevention literature indicates that predictive automation is advantageous in large verification systems with large event volumes, where pattern recognition is able to reduce manual complexity by over 30% [24]. The same improvement can be projected in hardware verification in case there is an injected force of adaptive agents in the UVM flow. The studies should also focus on building lighter structures used in testbenches that could cut down simulation overhead. Rapid UVM environments are currently in use, consuming more than 40% of total verification compute budgets in enterprise settings. Unloading this burden by trimming down the hierarchies of classes and more economical message delivery layers would increase the performance of operations with limited resources. The topic of error handling also needs to be better explored, with respect to root cause isolation when dealing with the complex design of SoC [25].

| Area of Focus                     | Improvement                                           | Potential Impact                                    |

|-----------------------------------|-------------------------------------------------------|-----------------------------------------------------|

| Adaptive Agents<br>Flow           | Reduce manual complexity by over 30%                  | Increase verification efficiency and speed          |

| AI-Driven<br>Generation           | Promote predictive automation in large systems        | Improve test coverage and reduce human intervention |

| Simulation<br>Reduction           | Cut down simulation overhead by optimizing structures | Increase performance with limited resources         |

| Error Handling<br>Cause Isolation | Enhance error handling in complex SoC designs         | Improve accuracy and reduce debugging time          |

Table 2: Focus Areas for Enhancing UVM Methodologies

# 6.2 Adoption in Smaller Companies

Small hardware companies are still hindered by tremendous obstacles to deploying UVM, mainly because of its costs and the complexity of implementation [26]. Studies must hence find the means of lowering the barrier to entry. Firms with fewer than fifty engineers can readily incorporate UVM with the aid of open training libraries, simplified starter kits, and low-cost cloud-based verification platforms without any significant restructuring. Across the history of semiconductor

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

### **Research Article**

startups taking place, case observations reveal that teams with small verification staff spend up to 20% of development time manually debugging. These inefficiencies would be minimized by the use of affordable UVM toolchains that would be enabled by community-based extensions. There is a need to study more on the economic trade-offs between complete UVM implementation and scenarios of partial hybrid verification models, particularly those companies engaged in low-volume lines of their products.

# 6.3 Machine Learning Exploration of UVM.

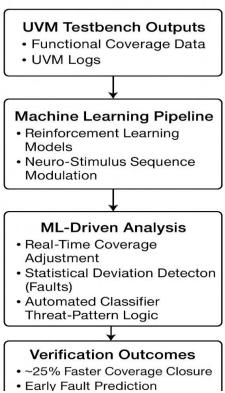

The perspective of automated test pattern generation lies in machine learning. Studies need to be carried out to determine how the models of reinforcement learning are able to track and modify the functional coverage outcomes and neuro-stimulus sequence modulation in real time. Initial industry experimentation sources claim that ML-assisted test creation would have the potential to cut the time to close coverage in extensive digital subsystems by nearly 25%. Early fault prediction with the assistance of ML methods is also possible by detecting statistical deviations in UVM logs. This approach conforms to the traditions of pattern-based threat detection in other domains of computing since automated classifiers are more responsive and risk-averse. The aspects of verification research must be based on the construction of credible pipelines with the integration of UVM outputs and ML analytics with traceability and safety [27].

Figure 7 below illustrates the integration of machine learning and UVM to improve the automated verification processes. UVM outputs, such as functional coverage penetration statistics and logistics analytics, are feed-forward to a machine learning process of relating test patterns on-the-fly to reinforcement learning and tailoring of neuro-stimulus sequence. The ML models identify statistical abnormality to aid in anticipating early faults and use classifier-based pattern analysis like threat-detection systems in computer applications. It is this integrated process that can close the covers in a faster manner, nearly by a quarter of the time, enhance the responsiveness, and help in building more secure, traceable, and reputable processes of verification among huge electronic sub-systems.

Figure 7: UVM verification workflow improvement through machine learning.

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

# **Research Article**

### 6.4 Higher-Order techniques of verification.

Cloud-based simulation and distributed regression systems will provide a vital direction for future development in UVM [28]. Most companies are already indicating that cloud scaling could decrease the time taken in regression completion by several days to below twelve hours. There should be research on how UVM components may be modified to operate effectively in those environments, especially in terms of synchronization and data transfer. More has to be done on mixed abstraction verification, which is a combination of transaction-based models and hardware acceleration. This combination may increase verification by over half in a high-performance computing design.

### 6.5 Addressing Research Gaps

There are still significant gaps in the general application of UVM [29]. Studies should find a solution to the sharp learning curve that intensely slows down the process of onboarding new verification engineers. Adoption would be enhanced by learning programs organized and by organized records. Further focus is needed to make sure that UVM conforms adequately to new tools, particularly AI-driven analysis systems. Researchers are advised to consider integration models that will enable a smaller company to use UVM without significant investments in infrastructure. Finally, the gaps will be filled with research that will enhance the quality of verification and contribute to the expansion of the industry's use.

As demonstrated in Figure 8 below, the photograph pictorially symbolizes the importance of eliminating research gaps. The triangle format focuses on the three important phases: Driving Innovation, where it outlines the need to identify gaps and create new developments; Advancing Knowledge, where gaps are addressed to increase knowledge on a given field; and Improving Practices, where the gaps help in creating more informed policies, interventions, and practices in the real world. These steps are critical within the scope of the UVM and indicate the necessity to solve the learning curve and the process of integrating the new tools, including the AI-powered analysis systems. Closures of these gaps will improve the effectiveness and quality of verification in the hardware industry [30].

Figure 8: The significance of addressing research gaps in UVM.

# Conclusions

The experimental data analysis of the research and the case studies show the immense importance of Universal Verification Methodology (UVM) in the hardware verification of the contemporary world. UVM has become a solid skeleton that enhances hardware verification operations in terms of efficacy, precision, and scale. The major conclusions indicate that UVM saves a considerable amount of time on verification, and companies like Intel and Qualcomm declared that it has a significant drop-in time spent on the verification of advanced hardware systems, up to 40 UVM modularity and automation have been shown to increase error detection by up to 25x. They are an invaluable asset to companies whose features include complex systems-on-chip (SoC) and multicore processor architectures. In addition, SystemVerilog, the base of UVM, continues to be a significant component of

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

# **Research Article**

hardware verification that has sophisticated capabilities, such as randomization and functional coverage, that help to strengthen verification environments. The paper sheds some light on the implementation of UVM into the processes of the industry, particularly the large semiconductor corporations, which have proven to be widely used and successful.

UVM has revolutionized the hardware verification reality, specifically in large-scale projects and startups. Introduction of UVM has standardized the workflow of verification, minimized human work, and made it feasible to learn more effective error detection. In the case of large organizations, such as Intel and AMD, UVM has resulted in shortened verification time and improved regression testing. These advantages will help in accelerated time-to-market and superior products. The smaller firms have also started to realize the benefits of UVM, but the high cost and complexity of the initial setup are still barriers. However, this could change with the continued use of the cloud-based solution and the use of cheaper toolchains, and UVM has a broader influence on more firms. The implications in the long term regarding the quality of the product are obvious: as UVM will allow automation of the test procedure and the increase of the number of detected errors, the possibility of post-launch problems is minimized, contributing to the higher trustworthiness of hardware products. Therefore, the time saved on verification can be used to generate quicker iterations and innovation, which keeps the companies at a competitive level in a rapidly changing market.

Hardware verification. The future of hardware verification is in the further development and adoption of UVM and SystemVerilog to more complex and automated verification models. Although the initial learning curve of UVM can be a challenge, the advantages of this tool in the long term, in terms of time, cost, and reduction of errors, are indispensable in the software verification of modern hardware. The potential of UVM is yet to be explored as more efficiencies and capabilities can be added to it, including machine learning and AI that would create automated test generation and predict faults, among others. As the complexity of hardware designs becomes more and more important, UVM will be an important part of the verification process, with which verification can keep up with the demands of modern hardware development. Future advances in hardware verification are likely to be pushed by the further development of UVM and its combination with alternative emerging technologies, and such advances will make the approach both more usable, efficient, and reliable in different fields.

### **References:**

- [1] David, J. B., & Chang, H. (2023). UVM Testbench Automation for AMS Designs. DVCON US.

- [2] Samala, S. (2024). Real-time Jira analytics: Integrating JQL with Power BI/Snowflake for predictive agile metrics. SciPubHouse. https://scipubhouse.com/home/international-journal-of-sustainability-and-innovation-inengineering-ijsie/content/ijsie-2024/real-time-jira-analytics-integrating-jql-with-power-bi-snowflake-for-predictive-agile-metrics/

- [3] Qamar, S., Butt, W. H., Anwar, M. W., Azam, F., & Khan, M. Q. (2020, February). A comprehensive investigation of universal verification methodology (UVM) standard for design verification. In *Proceedings of the 2020 9th International Conference on Software and Computer Applications* (pp. 339-343).

- [4] Moursi, A., Samhoud, R., Kamal, Y., Magdy, M., El-Ashry, S., & Shalaby, A. (2018, December). Different reference models for uvm environment to speed up the verification time. In *2018 19th International Workshop on Microprocessor and SOC Test and Verification (MTV)* (pp. 67-72). IEEE.

- [5] Height, H. (2012). A practical guide to adopting the universal verification methodology (UVM). Lulu. com.

2025, 10(5s) e-ISSN: 2468-4376

https://jisem-journal.com/

# **Research Article**

- [6] Baumann, R. (2005). Soft errors in advanced computer systems. *IEEE design & test of computers*, 22(3), 258-266.

- [7] Ziaee Bigdeli, A., Li, F., & Shi, X. (2016). Sustainability and scalability of university spinouts: A business model perspective. *R&D Management*, 46(3), 504-518.

- [8] Fiergolski, A. (2017). Simulation environment based on the Universal Verification Methodology. *Journal of Instrumentation*, 12(01), C01001.

- [9] Gundla, S. R. (2024). AI-optimized Kubernetes scheduling: Node affinity for Java microservices. SciPubHouse.

https://scipubhouse.com/home/international-journal-of-sustainability-and-innovation-inengineering-ijsie/content/ijsie-2024/ai-optimized-kubernetes-scheduling-node-affinity-for-java-microservices/

- [10] Gheisari, M., Panwar, D., Tomar, P., Harsh, H., Zhang, X., Solanki, A., ... & Alzubi, J. A. (2019). An optimization model for software quality prediction with case study analysis using MATLAB. *IEEE Access*, 7, 85123-85138.

- [11] Narayanan, A. (2012). *The emerging smart grid: Opportunities for increased system reliability and potential security risks* (Doctoral dissertation, Carnegie Mellon University).

- [12] NING, L. Z. (2015). Design and Application of Network-on-Chip Virtual Prototyping Platform.

- [13] Allmark, P., Boote, J., Chambers, E., Clarke, A., McDonnell, A., Thompson, A., & Tod, A. M. (2009). Ethical issues in the use of in-depth interviews: literature review and discussion. *Research Ethics*, 5(2), 48-54.

- [14] Ismail, K. A., & Ghany, M. A. A. E. (2021). Survey on Machine Learning Algorithms Enhancing the Functional Verification Process. Electronics 2021, 10, 2688.

- [15] Mohaidat, Z. R. M. (2019). *Study of Verification Techniques for Digital Architectures* (Doctoral dissertation, Politecnico di Torino).

- [16] Sayyed, Z. (2024). *Implementing automation with BPMN for margin call workflow*. IRJERNET. https://irjernet.com/index.php/fecsit/article/view/171

- [17] Vennamaneni, P. R. (2024). Delta Lake optimization techniques for scalable lakehouse architectures.

SciPubHouse. https://scipubhouse.com/home/international-journal-of-sustainability-and-innovation-inengineering-ijsie/content/ijsie-2024/delta-lake-optimization-techniques-for-scalable-lakehouse-architectures/

- [18] Salah, K. (2014, December). A UVM-based smart functional verification platform: Concepts, pros, cons, and opportunities. In *2014 9th International Design and Test symposium (IDT)* (pp. 94-99). IEEE.

- [19] Birnbaum, M. (2004). Essential electronic design automation (EDA). Prentice Hall Professional.

- [20] Solanki, R. B., Kulkarni, H. D., Singh, S., Verma, A. K., & Varde, P. V. (2018). Optimization of regression model using principal component regression method in passive system reliability assessment. *Progress in Nuclear Energy*, 103, 126-134.

- [21] Karhumaa, J. (2022). Analyzing UVM reuse (Master's thesis, J. Karhumaa).

- [22] Sinervä, M. (2023). *UVM testbench in Python: feature and performance comparison with SystemVerilog implementation* (Master's thesis, M. Sinervä).

- [23] Sultana, R. (2023). AI-Powered BI Dashboards In Operations: A Comparative Analysis For Real-Time Decision Support. *ASRC Procedia: Global Perspectives in Science and Scholarship*, 3(1), 62-93.

- [24] Hariharan, R. (2024). *API gateway threat prevention in large-scale applications*. SciPubHouse. https://scipubhouse.com/wp-content/uploads/2024/10/011-API\_gateway\_threat\_prevention\_in\_large-scale\_applications.pdf.

- [25] Chen, W., Ray, S., Bhadra, J., Abadir, M., & Wang, L. C. (2017). Challenges and trends in modern SoC design verification. *IEEE Design & Test*, 34(5), 7-22.

2025, 10(5s)

e-ISSN: 2468-4376

https://jisem-journal.com/ Research Article

- [26] Sutherland, S., & Fitzpatrick, T. (2015). Uvm rapid adoption: A practical subset of uvm. *Proceedings of DVCon*.

- [27] Yang, Y. (2019). A comprehensive topic-model based hybrid sentiment analysis system (Doctoral dissertation, Carleton University).

- [28] Walker, M. R. (2020). Assessment of Unmanned Aerial Systems and Lidar for the Utility Vegetation Management of Electrical Distribution Rights-of-Ways. West Virginia University.

- [29] Bromley, J. (2013, September). If SystemVerilog is so good, why do we need the UVM? Sharing responsibilities between libraries and the core language. In *Proceedings of the 2013 Forum on specification and Design Languages (FDL)* (pp. 1-7). IEEE.

- [30] Wile, B., Goss, J., & Roesner, W. (2005). *Comprehensive functional verification: The complete industry cycle*. Morgan Kaufmann.