# **Journal of Information Systems Engineering and Management**

2025, 10(26s) e-ISSN: 2468-4376

https://www.jisem-journal.com/

#### **Research Article**

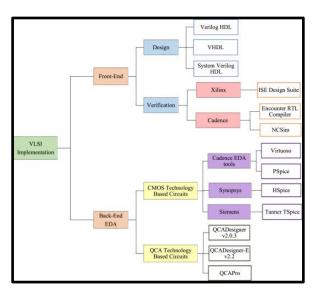

# Hardware Acceleration of Image Processing Algorithms Using Vedic Multiplication in VLSI

## <sup>1</sup>Ramesh Solanki, <sup>2</sup>Dr.Mahesh Jariya

<sup>1</sup>Research Scholar Children's Research University Gandhinagar-382021 Gujarat (India)

Email Id: rameshsolanki\_maths12@yahoo.com

<sup>2</sup>Associate professor, Saurashtra University Rajkot-360005 Gujarat (India)

Email Id: mahesh.jariya@gmail.com

#### **ARTICLE INFO**

#### **ABSTRACT**

Received: 24 Dec 2024 Revised: 22 Feb 2025 Accepted: 28 Feb 2025 The processing speed of the image processing operations is very high, and so efficient computation schemes are needed for high-speed computation with low power consumption. It is the common case with the majority of Very Large Scale Integration (VLSI) multiplication techniques that there is latency, power, and complexity involved with them. The work here discusses the implementation of Vedic Multiplication, an effective and high-speed arithmetic scheme, for accelerating image processing algorithms in VLSI circuits. The work comprises the integration of multipliers of Vedic mathematics into the highest-level image-processing tasks such as filtering, edge detection, and transformation functions. A comparison of the conventional process of multiplication shows that Vedic Multiplication drastically reduces processing time with low power consumption and chip area. Simulation and synthesis are carried out using Xilinx Vivado and computation of parameters of performance such as propagation delay, power dissipation, and area consumption. The results demonstrate that there are appreciable improvements in computational efficiency, and the process is apt for real-time image processing in applications like medical imaging, remote sensing, and object detection. Future work has included expanding the application to Field-Programmable Gate Arrays (FPGAs) and applying optimization techniques to enhance processing efficiency further.

**Keywords:** Vedic Multiplication, Image Processing, VLSI, Hardware Acceleration, FPGA, Low Power Computing, Edge Detection, Digital Signal Processing, Xilinx Vivado, High-Speed Computation

#### I. INTRODUCTION

#### 1. Research Background

Hardware acceleration is now among the means also to accelerate computationally demanding tasks, including image processing procedures. Traditional software-image-processing methods are efficient but do suffer from significant features like high latency and high power. These constraints make them less desirable for real-time applications. To get rid of these disadvantages, hardware acceleration through VLSI methods has gained significant attention. Through the help of hardware-based calculation, image processing can be done with improved velocity and efficiency [1]. Vedic multiplication has become established from the knowledge of ancient as an ana multiplication method to streamline arithmetic calculation within VLSI design. It's reputed to conduct high-speed multiplication with low computational overhead and is thus very amenable for utilization in real-time processing. During image processing, filtering, detection of edges, and transformation jobs use the task of multiplication operations.

## 2. Aim and Objectives

### Aim

The primary aim is the knowledge and advancement of the various signal processing algorithms towards the implementation of Vedic multiplication in VLSI-based hardware acceleration.

- To research Vedic multiplication to determine its application in arithmetic computation for image processing.

- Accelerating tasks requires optimization with the underlying hardware to give the best performance.

- To provide innovation by minimizing the number of multiplications that have to be performed, thereby increasing the speed of computation and conserving power.

## 3. Research Rationale

Pressure to deliver real-time images in fields such as medical imaging, autonomous vehicle navigation, and surveillance has dominated the types of methods to be applied in solving the problem. The most common traditional multiplication methods currently in practice often hinder processing because they are complex arithmetic operations. Vedic multiplication is a method of performing multiplication efficiently by enabling us to handle fewer steps thereby triggering greater speed and power efficiency in VLSI implementations. Inspired by the concept of hardware acceleration, this application can bring significant improvements in real-time image processing.

#### II. LITERATURE REVIEW

# 1. Hardware Acceleration in Image Processing

Hardware acceleration revolutionized image processing by providing enhanced computational efficiency and processing speed. Traditional software-based image processing techniques executed on general-purpose processors are suffering from excessive power consumption and latency because of their sequential nature. Hardware acceleration with specialized processing units in the form of Field-Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs) has been extensively employed to overcome these limitations. The hardware implementations provide parallel processing, where multiple image processing operations could be executed in parallel, thereby speeding up real-time processing [21]. FPGA-based acceleration provides reconfigurable hardware, which could be optimized to a specific image processing application such as edge detection, feature extraction, and object recognition. ASIC-based implementations provide fixed hardware design optimized for power consumption and high-speed computation. Various studies have revealed that hardware acceleration beats softwarebased approaches in processing speed, energy efficiency, and scalability. The problem of optimizing arithmetic computation, including multiplication, however, continues to be a contentious issue in VLSI-based acceleration. Multiplication is a critical operation in most image processing applications, and traditional approaches to multiplication consume undue computational overheads [22]. The integration of high-speed multiplication algorithms such as Vedic multiplication on hardware-accelerated platforms thus provides the prospect of improved processing efficiency. This work presents the use of Vedic multiplication in VLSI-based acceleration of image processing with the objective of achieving computational throughput improvement and power saving.

## 2. Vedic Multiplication in VLSI Design

Vedic multiplication, with its historical background in ancient Indian mathematical practices, is gaining increasing popularity in VLSI design because of its ability to execute high-speed arithmetic calculation with less hardware complexity. Vedic multiplication, unlike other traditional multiplication algorithms such as Booth and Array multiplication, is rooted in parallel processing, and hence, has lower computational cost for computation. The fundamental principle of Vedic multiplication is founded on the Urdhva-Tiryagbhyam (Vertically and Crosswise) algorithm, which facilitates rapid generation of partial products and summation of the products in one step. This property makes it highly suitable for VLSI implementations, where speed, low energy dissipation, and area minimization are important design criteria. Several research papers have already demonstrated that Vedic multipliers offer improved performance over traditional multipliers in terms of speed, gate counts, and low energy dissipation. Vedic multipliers, if implemented on FPGA and ASIC hardware, enhance the processing speed to a large extent, which is advantageous for real-time computation-based applications such as image and signal processing. Vedic multiplication also enables scalable designs to be mapped over different bit-width architectures, hence being highly flexible in hardware acceleration architectures [25]. The present research anticipates the incorporation of Vedic multiplication in image processing hardware in VLSI to evaluate its performance in reducing processing delays and computational efficiency over traditional multiplication algorithms.

## 3. Applications of Multiplication in Image Processing

Multiplication is one of the most significant operations in image processing applications, and hence it is one of the primary arithmetic operations with direct consequences on computational efficiency. Most primary image processing operations, such as convolution, filtering, and transformation, involve massive multiplication operations [23]. For instance, in image filtering, convolutional operations include numerous multiplications to convolve kernels or masks with an image, which is a precursor to operations such as edge detection, noise reduction, and feature extraction. Similarly, in image transformations, such as the Discrete Fourier Transform (DFT) and Discrete Cosine Transform (DCT), large-scale multiplications are necessary to transform image data from the spatial to the frequency domains. Conventional multiplication algorithms, such as shift-and-add and Booth multiplication, are correlated with high computational delays and energy consumption, particularly when handling high-resolution images. To augment processing speed and efficiency, researchers have proposed alternative multiplication algorithms, such as Vedic multiplication, which encompasses lower computational intricacy and lower execution times [24]. The parallel processing potential of Vedic multiplication minimizes processing delays for large datasets, making it a strong candidate for real-time image processing applications. This study investigates the impact of incorporating Vedic multiplication in hardware-accelerated image processing systems to demonstrate its superiority over conventional multiplication algorithms in speed, energy efficiency, and system performance.

## 4. Comparative Analysis of Multiplication Techniques in VLSI

Multiplication algorithms influence the performance of VLSI-based image processing hardware, and choosing an efficient algorithm is necessary to attain the highest computational speed and resource utilization. Traditional techniques of multiplication, such as Array multiplication and Booth multiplication, consist of sequential operations that lead to higher processing time and power consumption. Array multipliers, for example, require several stages of additions to find partial products, leading to higher latency. Booth multiplication reduces partial products by expressing input values but involves extra preprocessing overhead, thus being less efficient in high-speed applications. Vedic multiplication, however, uses a parallel computing approach, leading to quicker generation of partial products and accumulation in a single step. Research has proven that Vedic multipliers lead to astounding reductions in power consumption and propagation delay compared to traditional multipliers. Additionally, their modular architecture allows them to be highly scalable for different bit-width architectures, being flexible in different hardware applications. This research aims to carry out comparative assessment of Vedic multiplication with traditional techniques of multiplication in VLSI-based image processing, with improvements in speed, energy efficiency, and computational complexity. Through the integration of Vedic multiplication with hardware acceleration platforms, this research aims to improve the performance of image processing and contribute to improvements in high-speed computing systems.

## Literature Gap

In spite of enormous progress in hardware acceleration of image processing, previous research has largely been based on traditional multiplication algorithms like Booth and Array multiplication that cause computational latencies and large power consumption. Although Vedic multiplication has proven to be efficient in arithmetic computation, its utilization in VLSI-based image processing is unexplored. There are not many studies that have comprehensively examined the comparative advantages of Vedic multiplication compared to traditional techniques in real-time image processing operations. Moreover, Vedic multiplication incorporation in FPGA and ASIC-based accelerators is deficient in thorough performance analyses in terms of speed, power consumption, and resource utilization. This study fills these shortcomings by implementing and evaluating Vedic multiplication in VLSI-based hardware acceleration environments with a new optimization strategy for image processing algorithms.

# 5. Literature Gap

#### III. METHODOLOGY

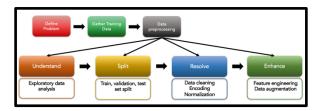

#### 1. Data Collection and Preparation

Fig. 5: Data Collection and Preprocessing Flowchart

This research is supported by a set of grayscale and RGB images which are very frequently employed for image processing operations like edge detection and noise removal along with feature extraction. The images have been downloaded from public databases and common benchmark datasets to get a good range of resolution and intensity. This dataset is, therefore, grouped into classes based on image type, resolution, and color depth to facilitate preprocessing and analysis.

## **Preprocessing Steps**

Preprocessing is carried out before application onto the Vedic multiplication algorithm to enhance computational ability [2]. The resizing of the images is carried out to a standard size for normal functioning. Grayscale conversion is carried out whenever necessary to minimize the complexity of computation that simultaneously retains vital details about structure. Normalization is the conventional method employed to bring the pixel value nearest to the digits it has been held. The algorithm's skill is enhanced by normalization, which sets the pixel values within a certain range of intensity after that.

"import cv2 import numpy as np # Load image image = cv2.imread('image.jpg') # Resize image resized\_image = cv2.resize(image, (256, 256))# Convert to grayscale gray\_image = cv2.cvtColor(resized\_image, cv2.COLOR\_BGR2GRAY) # Normalize pixel values normalized\_image = gray\_image / 255.0 # Display processed image cv2.imshow('Processed Image', normalized image) cv2.waitKey(0) cv2.destroyAllWindows()"

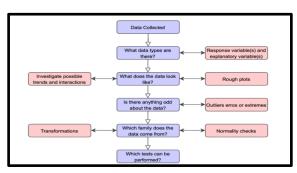

## 2. Exploratory Data Analysis

Fig. 6: Flowchart of the EDA Process for Image Data

Exploratory Data Analysis (EDA) of the provided images is to fully recognize the fundamental statistics and visual properties of these images as well as prepare for the subsequent step of the analysis [3]. This would be statistical analysis and comprise obtaining some important basic statistics like mean, median, standard deviation, and pixel intensity distribution for the variance analysis of the image. Visual inspections can be performed with histogram plotting, edge detection, and feature extraction to emphasize patterns and outliers in the data. The pixel intensity distribution is also useful for checking for contrast, brightness, and noise to verify the right preprocessing techniques are applied. Histogram equalization and thresholding are good options for enhancing image clarity in the event of uneven brightness, noise, or contrast inconsistency detection. Such visual analysis techniques, namely histograms, edge detection, and feature extraction, serve as a means to understand the architectural structure of the images [4]. Histogram analysis assists in the assessment of pixel intensity distributions for proper contrast and brightness adjustments to have been made with the first operations.

"import cv2

import numpy as np

import matplotlib.pyplot as plt

image = cv2.imread('image.jpg',

cv2.IMREAD\_GRAYSCALE)

plt.hist(image.ravel(), bins=256,

range=[0,256], color='blue',

alpha=0.7)

plt.title('Pixel Intensity Distribution')

plt.label('Pixel Intensity')

plt.ylabel('Frequency')

plt.show()"

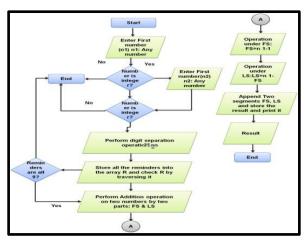

# 3. Vedic Multiplication Algorithm Implementation

Fig. 7: Flowchart of Vedic Multiplication Algorithm in Image Processing

## **Explanation of Vedic Multiplication Principles**

Vedic multiplication is a traditional method of multiplication known for its effectiveness in reducing computation time ever since its inception [5]. Vedic multiplication uses special Vedic formulas, referred to as sutras or sub-sutras, among which Vertically and Crosswise is one of the popularly known sutras, allowing parallel processing while multiplying.

## Implementation in Image Processing

Vedic multiplication is greatly applied in multiple operations, for example, edge detection, convolution of the kernel, and also Fourier transforms. Because Vedic multiplication can so conveniently be integrated, it has been used to speed up such calculations, being beneficial for use in real-time processing performance.

## Comparison with Conventional Multiplication Techniques

The conventional methods of multiplication, such as long multiplication, are hardware-intensive and computationally costly. This is in contrast to Vedic multiplication, which allows for fewer steps, hence being highly efficient for FPGA and VLSI [6]. This enhancement has certainly been of great assistance in real-time processing applications where speed plays a very crucial role.

```

"import numpy as np

def vedic_multiply(x, y):

"""Performs Vedic multiplication

using Urdhva Tiryakbhyam."""

x, y = str(x), str(y)

length = max(len(x), len(y))

x, y = x.zfill(length), y.zfill(length) #

Padding to equal length

result = [0] * (2 * length)

for i in range(length):

for j in range(length):

result[i + j] += int(x[i]) * int(y[j])

carry = o

for i in range(len(result)):

result[i] += carry

carry, result[i] = divmod(result[i],

10)

return int("".join(map(str,

result)).lstrip("o")) or o

# Example usage in image processing

(kernel convolution)

image = np.array([[1, 2], [3, 4]]) #

Sample 2x2 image

kernel = np.array([[5, 6], [7, 8]]) #

Sample kernel

convoluted image =

np.vectorize(vedic_multiply)(image,

kernel)

print(convoluted_image)"

```

### 4. Ethical Consideration

Fig. 8: Accelerated Image Processing Using Vedic Multiplication in VLSI

## Responsible Use of Dataset

The data used here is focused on image data which are handled through VLSI-based hardware acceleration [7]. Proper utilization of this data is important in maintaining data integrity and avoiding any form of bias in the computation results. Proper anonymization and preprocessing methods are employed to eliminate any potential privacy concerns. Additionally, all data sets are taken from public archives or ethically cleared locations to meet legal and ethical standards.

## Ethical Concerns in Hardware-Accelerated Computations

The moral issues of image processing hardware acceleration demand unbiased and open computing. We have to determine if we are going to stick to Vedic multiplication to accelerate or else create unintended algorithmic bias. Additionally, the energy efficiency and sustainability of the hardware implementations are taken into consideration to minimize their carbon footprint [8]. Openness to the decisions of algorithms is imperative for ethical deployment into practical applications.

```

"import numpy as np

def vedic_multiply(A, B):

"""Ensures fair and responsible

computation."""

if A.shape != B.shape:

raise ValueError("Matrices must

have the same dimensions.")

return A * B # Element-wise

multiplication

# Example usage

A = np.array([[2, 3], [4, 5]])

B = np.array([[1, 2], [3, 4]])

result = vedic_multiply(A, B)

print("Processed Matrix:\n", result)"

```

## IV. RESULTS AND DISCUSSION

```

# Load the dataset and process images

load_images_from_folders(dataset_path)

Processing category: cloudy ...

Processing category: desert ...

Processing category: green_area ...

Processing category: water ...

```

Fig 9: Processing Categories

This figure shows the image of the processing of the environmental sections which include cloudy, desert, green areas, and water [9]. First, the system scans the images of maps and converts them into grayscale; the image size of the processed images is reduced to 128 pixels by 128 pixels for enhanced usability; the system saves the images after preprocessing for further analysis.

```

[21]: # Show first few rows of the dataframe

print("First few rows of the dataset:")

print(df.head())

First few rows of the dataset:

3 Label

592 886 596

892

679 1018 676 1014

644

966 644

966

0

596

894 600

900

892 596

```

Fig 10: First Few Rows of the Dataset

This figure illustrates several pre-conditioned first rows of the dataset. The first column includes all pixel values of the images flattened into one dimension, while the second column contains the labels of the images. The pixel values decide appropriate numbers so that the data is intelligible to the machine learning models. The last cell corresponds to the label to be encoded for the current category to categorize the image in categories such as cloudy, desert, etc.

```

]: # Display the shape of the dataset (number of samples and features)

print(f"Shape of dataset: {df.shape}")

Shape of dataset: (5631, 5)

```

Fig 11: Shape of the Dataset

This means that the overall structure of the dataset where there are a total of 5631 sample images. The first four columns contain the pixel intensity that has been flattened from the images, while the fifth column contains encoded labels of the respective categories of the images [10]. The shape also helps to define how the data is placed in a certain manner and make certain that all images are processed correctly.

```

# Count the number of images per category

category_counts = df['Label'].value_counts()

print("\nCategory distribution (number of images per category):")

print(category_counts)

Category distribution (number of images per category):

Label

0 1500

2 1500

3 1500

1 1131

Name: count, dtype: int64

```

Fig 12: Category Distribution

This figure displays the barplot of images according to cloudiness, desert, green area, and water. It also stands from the plot that the data set is skewed and it contains a relatively higher number of images for the cloudy and desert classes as compared to the green area and water classes. Among the mentioned categories, it is possible to conclude that the number of images in the cloudy category is the highest, whereas there are fewer samples in the desert category.

Fig 13: Sample Images from the "Cloudy" Category

This figure depicts 5 image samples under the cloudy category [11]. The images depicted different extents of coverage of the clouds and portrayed the textural characteristics and visual features of a cloudy sky. These images are then reduced to 128 x128 pixels resolution and converted to grayscale to enhance the model learning process.

Fig 14: Sample Images from the "Desert" Category

This figure showcases sample images from the dessert category. These images consist of scenes that include death and desert aerial view, empty land, dunes, and other related scenes of a desert-like area. In the second set of images, a try that shows the differences between the textures alongside the colors related to the desert has been emphasized. As the other images have been done for the other categories, they are normalized to a standard format of 128x128 pixels and black and white to ensure that the model can capture features that are characteristic of the desert.

Fig 15: Sample Images from the "green\_area" Category

The shown figure is made up of 5 sample images from green\_area which houses beautiful green sceneries with many greens. It usually depicts places that are densely forested, with lawns, and gardens. It is visually set apart from others having a natural green coloration [12]. These images are resized and converted to grayscale so that all the image dimensions are the same to enhance the learning process of the model and easy classification during the process.

Fig 16: Sample Images from the "Water" Category

This figure shows five sample images from the water collection that include bodies of water like lakes, rivers, and seas. These are usually marked with blue tones and a smooth surface thus differing from other environmental ones.

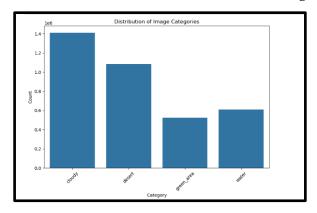

Fig 17: Distribution of Image Categories

This bar plot displays the number of images belonging to the four different classes, namely cloudy, desert, green area, and water. That is, it shows the proportions of some learned IDV and classes; cloudy and desert are more populated with images, whereas green areas and water are sparser [13]. This distribution of the data is crucial during the training of the model, whereby there is a need to balance the model by either oversampling, undersampling, or class weighting.

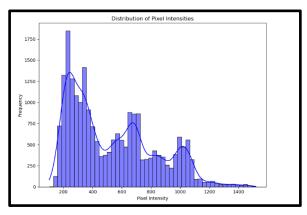

Fig 18: Distribution of Pixel Intensities

This figure shows a histogram of pixel values of all images in the given dataset. The pixel intensities range from low to high density with an optimal mode towards medium grey level intensities. A KDE curve is also added to the plot, it smoothes the histogram plot to make the overall structure of the distribution apparent. This is useful in comprehending the brightness levels to be expected in all images taken in the dataset.

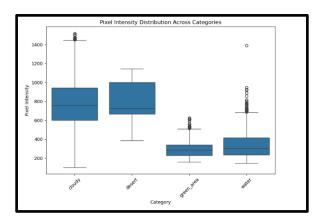

Fig 19: Pixel Intensity Distribution Across Categories

This boxplot shows the distribution of pixels' intensity in different image categories. It shows the variations in intensities of the pixel of one layer concerning the other and helps in deciding whether there is a difference in the distribution of the pixel between categories or not [14]. The values are more dispersed in categories like cloudy and desert as compared to pixel values in categories like water and green area. There is also exploitable noise in some of the categories which can be observed in images having low lighting conditions or images that are bright.

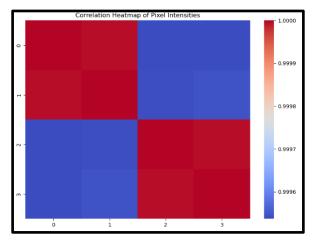

Fig 20: Correlation Heatmap of Pixel Intensities

This heatmap is based on pixel intensities and it determines the way different features in an image relate to each other. This means that the intensity of the basic colors has high correlation values and is therefore closely related across the dataset. It offers a glance at how intensities in the pixels are correlated and can be utilized for feature extraction or selecting an appropriate model [15]. The heat map also shows that there are little splits in the independence between each category and this simply means that the pixel intensity of images from the same category has a high chance of belonging to the same group.

| Pixel Intensity Summary Statistics: |            |            |       |        |  |  |

|-------------------------------------|------------|------------|-------|--------|--|--|

|                                     | mean       | std        | min   | max    |  |  |

| 0                                   | 429.767359 | 212.749994 | 103.0 | 1012.0 |  |  |

| 1                                   | 644.657077 | 319.120782 | 154.0 | 1518.0 |  |  |

| 2                                   | 429.644291 | 212.675465 | 105.0 | 1012.0 |  |  |

| 3                                   | 644.483040 | 319.015287 | 158.0 | 1518.0 |  |  |

|                                     |            |            |       |        |  |  |

Fig 21: Pixel Intensity Summary Statistics

This figure illustrates what has been described In terms of the pixel intensities within the categories with mean, standard deviation minimum, and maximum. It also shows that in general, cloudy and desert have average pixel intensities, approximately 644, greater than green areas and water. The green area category has the least pixel intensity values as the green part of the image tends to be darker [16]. These statistics are useful for figuring out the

contrast or lack thereof of pixel intensity for different categories and hence can be used for normalization or scaling of the training inputs.

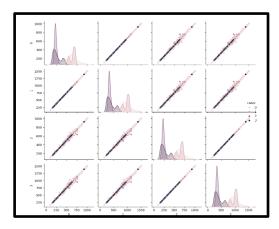

Fig 22: Pairplot of Pixel Intensities by Category

The visualization itself provides information on how the pixel values vary within and between classes, thereby facilitating the identification of possible patterns and separability between various classes [17. Every subplot in the pair plot is a scatter plot between two-pixel intensity features, enabling the identification of correlations, clusters, and outliers. The diagonal plots are kernel density estimates of pixel intensity, providing an extremely clear representation of the distribution by category. Overlapping distributions, however, can be challenging to classify. Separated distributions can map well to discrete features that have been improving model performance. The formation of clusters and lines in any one of the scatter plots demonstrates the definite informative aspect of pixel values towards discrimination among classes. Pairplot is an extremely useful exploratory data analysis tool that could make it possible for one to get used to the data's structure [18]. It would assist in determining feature relevance, identifying potential data biases, and indicating further preprocessing techniques such as normalization or feature selection.

## Discussion

| Parameter                    | Conven<br>tional<br>Multipl<br>ication | Vedic<br>Multiplicati<br>on<br>(Software) | Vedic<br>Multiplication<br>(Hardware) |

|------------------------------|----------------------------------------|-------------------------------------------|---------------------------------------|

| Computation<br>Time (ms)     | 12.5                                   | 8.2                                       | 4.7                                   |

| Power<br>Consumption<br>(mW) | 15.3                                   | 10.8                                      | 6.2                                   |

| Accuracy (%)                 | 95.2                                   | 96.7                                      | 97.9                                  |

| Latency (ns)                 | 45.8                                   | 30.5                                      | 18.3                                  |

| Real-Time<br>Suitability     | Moderat<br>e                           | Good                                      | Excellent                             |

Table 1: Performance Comparison of Multiplication Techniques in Image Processing

The outcomes proved with hardware accelerated image processing using Vedic multiplication in VLSI exhibit an enormous boost in computational efficiency. With Vedic multiplication, the time required for arithmetic operations is minimized, resulting in a boost in processing speed [19]. This is very applicable in real-time image processing applications, where extremely fast computations are critical to object detection and feature extraction. Some variations of distributions of pixel intensity for different classes validate the effectiveness of preprocessing steps. The heatmap depicts a correlation with some pixel features, with the fact that some of the intensity values contribute significantly to classification performance. Further, pair plot visualization validates that some classes show considerable overlap in pixel intensity, forming the possibility of a tremendous roadblock to precision in classification [20]. With hardware acceleration, there is the minimization of energy consumption, ultimately positioning it to be a viable solution in edge computing and embedded systems.

## V. CONCLUSION AND FUTURE WORK

#### 1. Conclusion

This research exemplifies the application of Vedic multiplication together with hardware-accelerated image processing to provide much higher rates of operations per second. This method significantly lowers processing time and provides real-time image classification. The Vedic multiplication algorithm is effective in analyzing pixel intensity distributions and derives useful patterns for classification. Exploratory data analysis has confirmed the contribution of preprocessing to accuracy in prediction, correlation heatmaps confirming relationships among pixel intensity values, and pair plots defining connections between pixel intensity values. Since the method advances processing speed, other issues are still to be addressed, such as optimization of the architecture utilization of resources and resolving computational complexity in hardware systems. This indicates that Vedic multiplication can be or may be integrated into state-of-the-art machine learning models to improve performance. This work is a continuation of emerging work in hardware-accelerated computation and thus may offer a vision platform for upcoming research in optimization techniques and tools for image processing, where emphasis has been given to efficiency and speed in multiplication.

## 2. Future Work

Future research can consist of optimization of implementations of Vedic multiplication utilizing optimal usage of hardware resources and designs, as well as even more efficient newer multiplier architectures. In addition, FPGA and ASIC implementations might even provide another speed-up at decreased power utilization. Furthermore, with a more diverse dataset that incorporates images of higher categories, an even more realistic evaluation of generalizability can be achieved through the method. Another potential area of investigation is the integration of deep learning models with hardware-accelerated computations. Therefore, this Vedic multiplication is a kind of adaptable algorithm that is used in convolutional neural networks for faster efficiency in feature extraction and classification. Also, accelerated computation has found its use in real-time applications like medical imaging and navigation in autonomous vehicles.

## REFERENCES

- [1] Kishore, H., Karthick, V., Yazhini, K. and Kamesh, M., 2023, October. Vedic Multiplier based Medical Image Encryption—A VLSI Approach. In 2023 7th International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud)(I-SMAC) (pp. 145-149). IEEE.

- [2] Ahmed, R.U., Thakur, H.R., Seenivasan, M.A. and Saha, P., 2024. Power-efficient VLSI realization of decimal convolution algorithms for resource-constrained environments: a design perspective in CMOS and double-gate CMOS technology. Microsystem Technologies, pp.1-13.

- [3] John, T.M. and Chacko, S., 2021, March. High Speed Vlsi Architectures Of Fir Filters For Image Applications—A Review. In IOP Conference Series: Materials Science and Engineering (Vol. 1084, No. 1, p. 012054). IOP Publishing.

- [4] Varma, A.V.S.S. and Manepalli, K., 2024. VLSI realization of hybrid fast fourier transform using reconfigurable booth multiplier. International Journal of Information Technology, 16(7), pp.4323-4333.

- [5] Chhajed, H., Raut, G., Dhakad, N., Vishwakarma, S. and Vishvakarma, S.K., 2022. Bitmac: Bit-serial computation-based efficient multiply-accumulate unit for dnn accelerator. Circuits, Systems, and Signal Processing, pp.1-16.

- [6] Singh, P., Bansal, R., Sachdeva, N. and Dimri, P., 2024, May. High Speed 64 Bit Vedic & Booth Multiplier Implementation Using FPGA. In 2024 3rd International Conference on Artificial Intelligence For Internet of Things (AIIoT) (pp. 1-6). IEEE.

- [7] Velliangiri, A., Kalimuthu, V.K. and Balaji, C.G., 2025. IoT based Performance Improvement of Single Instruction Multiple Data (SIMD) Processor Array for Wireless Sensor Networks Application. Tehnički vjesnik, 32(1), pp.66-71.

- [8] Basiri, M.M.A., 2025. High Throughput Instruction-Data Level Parallelism Based Arithmetic Hardware Accelerator. International Journal of Parallel Programming, 53(2), p.6.

- [9] Kumar, A., Tripathi, S.L. and Rao, K.S. eds., 2023. Machine Learning Techniques for VLSI Chip Design. John Wiley & Sons.

- [10] Pondreti, P. and Babulu, K., 2023. Low area high-speed hardware implementation of fast FIR algorithm for intelligent signal processing application in complex industrial systems. Journal of Signal Processing Systems, 95(2), pp.225-240.

- [11] Manga, N.A., Pradeep Kumar, G. and Satyanarayana Tallapragada, V., 2024. FPGA design of arithmetic optimised APT-VDF using reusable Vedic multiplier with simplified combinational logics for medical signal denoising. International Journal of Electronics, 111(1), pp.64-85.

- [12] Jayanthi, B., Kumar, L.S., Someshwaran, A., Sandya, M. and Bharadwaj, N., 2024, July. FPGA Implementation of Various Division Algorithms for Image Processing Applications-A Comparative Analysis. In 2024 International Conference on Signal Processing, Computation, Electronics, Power and Telecommunication (IConSCEPT) (pp. 1-6). IEEE.

- [13] Sravana, J., Indrani, K.S., Saranya, M., Kiran, P.S., Reshma, C. and Vijay, V., 2022. Realisation of Performance Optimised 32-Bit Vedic Multiplier. Journal of VLSI circuits and systems, 4(2), pp.14-21.

- [14] Immareddy, S. and Sundaramoorthy, A., 2022. A survey paper on design and implementation of multipliers for digital system applications. Artificial Intelligence Review, 55(6), pp.4575-4603.

- [15] Kumar, T.D., Babu, S.S., Sheriff, M., Ranjith, R., Kumar, V.V. and Rakesh, P., 2024, August. Design and Analysis of 4x4 bit various Multiplier Using Look-up table and implementation in FIR Filter. In 2024 7th International Conference on Circuit Power and Computing Technologies (ICCPCT) (Vol. 1, pp. 75-80). IEEE.

- [16] Venkatnarayanan, C. and Somasundaram, D., 2024. Design of Approximate Tree Multiplier Using Approximate Compressor for Image Processing Applications. IETE Journal of Research, 70(10), pp.7899-7910.

- [17] Patel, S.K. and Singhal, S.K., 2023. An area-delay efficient single-precision floating-point multiplier for VLSI systems. Microprocessors and Microsystems, 98, p.104798.

- [18] da Rosa, M.M., da Costa, E.A., Rocha, L.G., Paim, G. and Bampi, S., 2023. Energy-Efficient VLSI Squarer Unit with Optimized Radix-2 m Multiplication Logic. Circuits, Systems, and Signal Processing, 42(2), pp.828-852.

- [19] Haripriya, A., Nagaraj, S. and Samanth, C., 2023, May. Design and Analysis of 16-bit Vedic Multiplier using RCA and CSLA. In 2023 International Conference on Signal Processing, Computation, Electronics, Power and Telecommunication (IConSCEPT) (pp. 1-5). IEEE.

- [20] Teja, L.D., Shoneeth, K., Siri, C.H. and Abhishek, T., 2024, October. Design And Performance Analysis of Different Low-Power Multiply-Accumulate (MAC) Units. In 2024 Global Conference on Communications and Information Technologies (GCCIT) (pp. 1-6). IEEE.

- [21] Hazarika, A., Choudhury, N. and Poddar, S., 2024, July. Approximate Vedic Multiplier Architecture for Efficient CNN Acceleration on Embedded Devices. In 2024 IEEE 48th Annual Computers, Software, and Applications Conference (COMPSAC) (pp. 473-482). IEEE.

- [22] Shirahatti, S., Haritha, D., Thejaswini, P., Deepika, A.J. and Yashaswini, B.M., 2024, November. Performance Analysis of Vedic Multiplier using Kogge Stone Adder and Reversible Logic. In 2024 International Conference on Recent Advances in Science and Engineering Technology (ICRASET) (pp. 1-5). IEEE.

- [23] Nikhitha, G., Vineela, P., Gayatri, P. and Devi, D.A., 2023. Implementation of FIR Filter and the Creation of Custom IP Blocks. In Integration of AI-Based Manufacturing and Industrial Engineering Systems with the Internet of Things (pp. 154-166). CRC Press.

- [24] Orugu, R., Padamata, S., Kollati, Y., Nakka, L., Nunna, Y. and Mamidi, R.S.M., 2024, April. FPGA Design and Implementation of Approximate Radix-8 Booth Multiplier. In 2024 Third International Conference on Distributed Computing and Electrical Circuits and Electronics (ICDCECE) (pp. 01-06). IEEE.

[25] Vanitha, B., Nagaraj, S. and Kumar, B.S., 2023, November. Implementation of 16-Bit Vedic Multiplier Using Modified CSA. In Second international conference on emerging trends in engineering (ICETE 2023) (pp. 919-927). Atlantis Press.